Z80 PIO

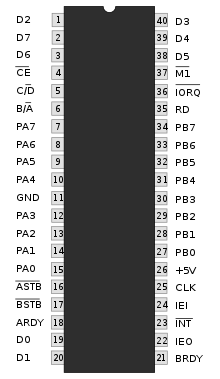

Z80 PIO (Z80 Parallel Input/Output) je integrovaný obvod z rodiny procesoru Z80. Jedná se obvod poskytující dvě paralelní osmibitové brány (obvykle označované jako brána A a brána B). Díky tomu umožňuje plně využívat možnosti systému přerušení procesoru Z80. Podobný obvod v rodině procesoru Intel je obvod Intel 8255. Obvod je použit v interfacu pro připojení AMX mouse k ZX Spectru.[1] Je také základem českého interfacu Mirek.

Režimy paralelních bran[editovat | editovat zdroj]

Brány mohou pracovat v následujících režimech:

- režim vstupu,

- režim výstupu,

- obousměrný režim (v obousměrném režimu může pracovat pouze brána A),

- bitový režim

V režimu vstupu, jakmile je obvod připraven k příjmu dat, je aktivován signál RDY. Poté obvod čeká na aktivaci signálu /STB. Jakmile je tento aktivován, načte data přítomná na vstupu a přečtení dat potvrdí deaktivací signálu RDY. Podle nastavení obvodu se přijetí dat může aktivovat přerušení.

V režimu výstupu je po zápisu dat na výstup aktivován signál RDY. Po té obvod čeká na potvrzení přečtení dat signálem /STB. Podle nastavení obvodu se po přijetí potvrzení o přečtení dat může aktivovat přerušení.

Obousměrný režim je kombinací vstupního a výstupního režimu. V tomto režimu může pracovat pouze brána A, protože k potvrzování přítomnosti výstupních dat jsou použity signály /STB a RDY brány A (/ASTB a ARDY) a k potvrzování přijetí vstupních dat jsou používány signály /STB a RDY brány B (/BSTB a BRDY). Pokud brána A pracuje v obousměrném režimu, brána B musí pracovat v bitovém režimu.

V bitovém režimu nejsou používány signály /STB a RDY. V tomto režimu je možné nastavit, které bity příslušné brány budou vstupní a které výstupní. Také je možné nastavit podmínku, při jejíž splnění bude aktivováno přerušení.

Konfigurace obvodu[editovat | editovat zdroj]

Konfigurace obvodu probíhá pomocí konfigurační brány, každá brána má svojí konfigurační bránu.

Nastavení režimu[editovat | editovat zdroj]

| Nastavení režimu brány | ||||||||

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| režim brány | 1 | 1 | 1 | 1 | ||||

Režim brány může být 00 – výstupní režim, 01 – vstupní režim, 10 – obousměrný režim, 11 – bitový režim. Je-li nastaven bitový režim, je nutné na konfigurační bránu poslat ještě druhý byte, jehož bity určí, který bit brány bude vstupní a který výstupní (0 – výstupní, 1 – vstupní).

Nastavení přerušení[editovat | editovat zdroj]

K povolení či zakázání přerušení lze použít zjednodušené nebo úplné nastavení. Zjednodušené nastavení pouze povoluje či zakazuje generování přerušení. Úplným nastavením se navíc nastavuje podmínka generování přerušení v bitovém režimu.

| Zjednodušené nastavení přerušení | ||||||||

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| povolení přerušení | 0 | 0 | 1 | 1 | ||||

| Úplné nastavení přerušení | ||||||||

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| povolení přerušení | AND/OR | 1/0 | maska | 0 | 1 | 1 | 1 | |

Generování přerušení může být buď zakázáno (0) nebo povoleno (1). Příznakem AND/OR je nastavováno za v bitovém režimu pro generování přerušení je nutné, aby byly aktivní všechny bity brány (1) nebo zda postačuje aktivita alespoň jednoho bitu brány (0). Příznak 1/0 nastavuje, zda je bit brány aktivní v log. 1 nebo v log. 0. Pokud pro generování přerušení mají být použity pouze některé bity, je nutné nastavit na log. 1 příznak maska. Po té je očekáván ještě jeden byte, jehož bity určí, které bity brány budou generovat přerušení (0 – generuje přerušení, 1 – negeneruje přerušení).

Než je povoleno přerušení, je nutné nastavit vektor přerušení, který bude odesílán procesoru.

| Vektor přerušení | ||||||||

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| vektor přerušení | 0 | |||||||

Reference[editovat | editovat zdroj]

- ↑ Amiga Mouse, Atari Mouse, AMX Mouse, AY Mouse na velesoft.speccy.cz

Literatura[editovat | editovat zdroj]

- Jan Smrž (MSP) a Jaromír Krejčí. Tipy na čipy II. ZX Magazín. 1995, čís. 2/95, s. 20. ISSN 1210-4833.

Externí odkazy[editovat | editovat zdroj]

Obrázky, zvuky či videa k tématu Z80 PIO na Wikimedia Commons

Obrázky, zvuky či videa k tématu Z80 PIO na Wikimedia Commons - Zilog Z80 PIO User's Manual na z80.info

- Z80 PIO na CPCWiki